组合逻辑电路

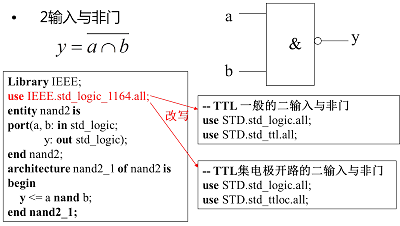

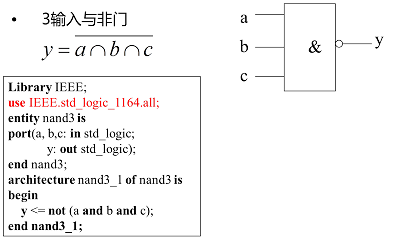

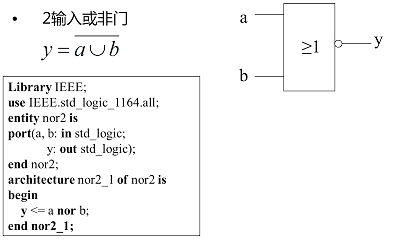

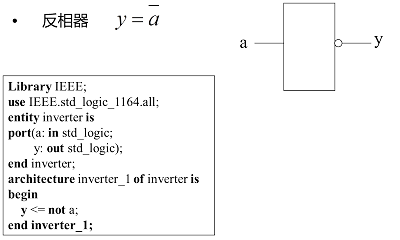

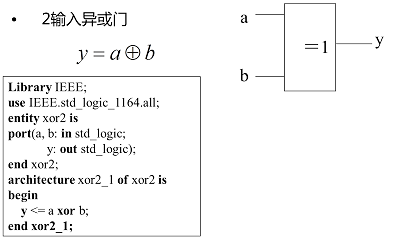

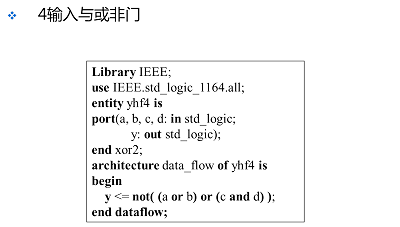

(1)简单门电路

(2)编、译码器与选择器

普通编码器

8-3编码器,对输入的8个信号进行编码操作,然后在输出端以3位二进制码的形式进行输出,输入信号低电平有效。以下描述为普通编码器,不具有优先级:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY encoder8-3 IS

PORT(d : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

q : OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END encoder8-3;

ARCHITECTURE rtl OF encoder8-3 IS

BEGIN

PROCESS(d)

BEGIN

CASE d IS

WHEN “01111111”=> q<=“111” ;

WHEN “10111111”=> q<=“110” ;

WHEN “11011111”=> q<=“101” ;

WHEN “11101111”=> q<=“100” ;

WHEN “11110111”=> q<=“011” ;

WHEN “11111011”=> q<=“010” ;

WHEN “11111101”=> q<=“001” ;

WHEN “11111110”=> q<=“000” ;

WHEN OTHERS=> q<=“XXX” ;

END CASE;

END PROCESS;

END rtl;

优先级编码器(74LS148)

当多个输入有效时,按优先级输出:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY encoder83 IS

PORT( input: IN STD_LOGIC_VECOR(7 DOWNTO 0);

y: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END encoder83;

ARCHITECTURE rtl OF encoder83 IS

BEGIN

PROCESS(input)

BEGIN

IF input(0)='0' THEN y<="111";

ELSIF input(1)='0' THEN y<="110";

ELSIF input(2)='0' THEN y<="101";

ELSIF input(3)='0' THEN y<="100";

ELSIF input(4)='0' THEN y<="011";

ELSIF input(5)='0' THEN y<="010";

ELSIF input(6)='0' THEN y<="001";

ELSE y<= "000";

ENDIF;

END PROCESS;

END rtl;

变量译码器

3-8译码器(74LS138):

3个选通输入端:

g1&g2a&g2b= '100',

正常译码,低电平有效;

否则,y0~y7输出均为高电平。

3-8译码器实现:

Library IEEE;

use IEEE.std_logic_1164.all;

entity decoder38 is

port(a, b, c, g1, g2a, g2b: in std_logic;

y: out std_logic_vector(7 downto 0));

end decoder38;

ARCHITECTURE rtl OF decoder38 IS

SIGNAL indata: STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

indata<=c&b&a;

PROCESS(indata, g1, g2a, g2b)

BEGIN

if(g1=='1' and g2a='0' and g2b='0') then

CASE indata IS

WHEN “000” => y<=“11111110”;

WHEN “001” => y<=“11111101”;

WHEN “010” => y<=“11111011”;

WHEN “011” => y<=“11110111”;

WHEN “100” => y<=“11101111”;

WHEN “101” => y<=“11011111”;

WHEN “110” => y<=“10111111”;

WHEN “111” => y<=“01111111”;

WHEN others => y<=“XXXXXXXX”;

END CASE;

else

y<=“11111111”;

end if;

END PROCESS;

END rtl;

码制变换译码器

4-10线译码器:

4输入a、b、c、 d

10输出y0、y1、y2、y3、y4、y5、y6、y7、y8、y9

地址译码器

将译码器输入端的输入地址信号翻译成相应的输出控制信号。典型应用:根据输入端的不同地址输入信号,经过译码后选择不同的存储空间。

4选1选择器:

Library IEEE;

use IEEE.std_logic_1164.all;

entity mux4 is

port(i0,i1,i2,i3: in std_logic_vector(3 downto 0);

a, b: in std_logic

y: out std_logic);

end mux4;

architecture rtl of mux4 is

signal sel:std_logic_vector(1 downto 0);

begin

sel<=b &a;

process(sel)

begin

IF sel="00" then f<=i0;

ELSIF sel="01" then f<=i1;

ELSIF sel="10"then f<=i2;

ELSE f<=i3;

END IF;

end process;

end rtl;

或者:

case sel is

when “00” => f<=i0;

when “01” => f<=i1;

when “10” => f<=i2;

when “11” => f<=i3;

when others => null;

end case;

或者采用条件信号代入语句:

BEGIN

sel<=B&A;

f<=i0 WHEN sel=“00” ELSE

i1 WHEN sel=“01” ELSE

i2 WHEN sel=“10” ELSE

i3 WHEN sel=“11” ELSE

'X';

END rtl;

或者采用选择信号代入语句:

BEGIN

sel<=B&A;

WITH sel SELECT

f<=i0 WHEN sel=“00”,

i1 WHEN sel=“01”,

i2 WHEN sel=“10”,

i3 WHEN sel=“11”,

'X' WHEN OTHERS;

END rtl;

(3)加法器、求补器、比较器

半加器:

Library IEEE;

use IEEE.std_logic_1164.all;

entity half_adder is

port(a, b: in std_logic;

s, co: out std_logic);

end half_adder;

architecture half1 of half_adder is

signal c, d: std_logic;

begin

c<= a or b;

d<= a nand b;

co<= not d; -- a and b;

s<= c and d; -- a xor b;

end half1;

全加器(由两个半加器构成):

Library IEEE;

use IEEE.std_logic_1164.all;

entity full_adder is

port(a, b, cin: in std_logic;

s, co: out std_logic);

end full_adder;

architecture full1 of full_adder is

component half_adder

port(a, b: in std_logic;

s, co: out std_logic);

end component;

signal u0_co, u0_s, u1_cod: std_logic;

begin

u0: half_adder port map( a,b,u0_s,u0_co);

u1: half_adder port map( u0_s,cin,s,u1_co);

co<= u0_co or u1_co;

end full1;

求补器:求反加一,x7和y7是符号位。

Library IEEE;

use IEEE.std_logic_1164.all;

entity hosuu is

port(x: in std_logic_vector(7 downto 0);

y: out std_logic_vector(7 downto 0));

end hosuu;

architecture rtl of hosuu is

begin

y<= not x + '1';

end full1;

比较器:对两个4位二进制数进行比较,其中A和B分别是参与比较的两个4位二进制数,YA、YB和YC是用来分别表示A>B、A<B和A=B的3个输出端。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY comp4_v1 IS

PORT(A: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

B: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

YA,YB,YC: OUT STD_LOGIC);

END comp4_v1;

ARCHITECTURE behave OF comp4_v1 IS

BEGIN

PROCESS (A,B)

BEGIN

IF (A > B) THEN

YA <='1';

YB <='0';

YC <='0';

ELSIF(A < B) THEN

YA <='0';

YB <='1';

YC <='0';

ELSE

YA <='0';

YB <='0';

YC <='1';

END IF;

END PROCESS;

END behave;

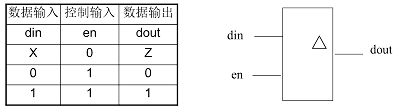

(4)三态门及总线缓冲器

三态门和双向缓冲器是接口电路和总线驱动电路的常用器件。

三态门电路:

Library IEEE;

use IEEE.std_logic_1164.all;

entity tri_gate is

port(din, en: in std_logic;

dout: out std_logic);

end tri_gate;

architecture zas of tri_gate is

begin

tri_gate1:process(din, en)

begin

if (en='1') then

dout<=din

else

dout<='Z';

end if;

end process;

end zas;

或者:

architecture blk of tri_state is

begin

tri_gate2: block(en='1')

begin

dout<=guarded din;

end process;

end blk;

或者:

architecture nas of tri_state is

begin

tri_gate2: process( din, en)

begin

case en is

when '1'=>dout<=din;

when others=>dout<='Z';

end case;

end process;

end nas;

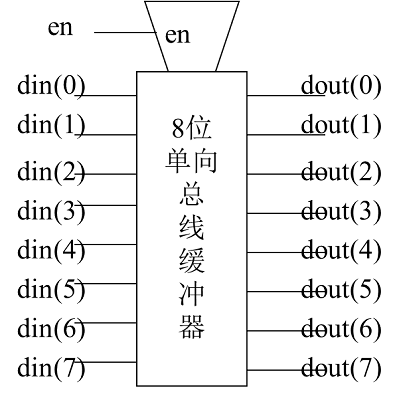

单向总线缓冲器:由多个三态门组成,用于驱动地址总线和控制总线。由单一控制端en控制。

Library IEEE;

use IEEE.std_logic_1164.all;

entity tri_buf8 is

port(din: in std_logic_vector(7 downto 0);

en: in std_logic;

dout: out std_logic_vector(7 downto 0));

end tri_buf8;

architecture zas of tri_buf8 is

begin

tri_buf1: process(din, en)

begin

if (en='1') then

dout<=din

else

dout<="ZZZZZZZZ";

end if;

end process;

end zas;

注意:

1)Z不能赋予变量;

2)Z与0、1不能混合赋值;如

dout<="Z0Z10ZZZ";

3) 但是可以分开赋值,如

dout(0)<='Z';

dout(1 to 3)<="101";

dout(4 to 7)<="ZZZZ";

多种构造体实现:

architecture blk of tri_buf8e is

begin

tri_buf2: block(en='1')

begin

dout<=guarded din;

end process;

end blk;

或者:

architecture nas of tri_buf8 is

begin

tri_gate3: process( din, en)

begin

case en is

when '1'=>dout<=din;

when others=>dout<= "ZZZZZZZZ";

end case;

end process;

end nas;

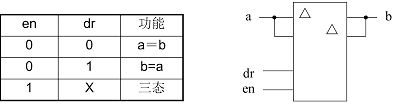

双向总线缓冲器:用于对数据总线的驱动和缓冲。

两个数据输入/输出端:a和b

一个方向控制端:dr

一个选通端:en。

Library IEEE;

use IEEE.std_logic_1164.all;

entity tri_bigate is

port(a, b: inout std_logic_vector(7 downto 0);

en, dr : in std_logic);

end tri_bigate;

architecture rtl of tri_bigate is

signal aout,bout: std_logic_vector(7 downto 0);

begin

process( a, dr, en)

begin

if (en='0') and (dr='1') then bout<=a;

else bout<="ZZZZZZZZ";

end if;

b<=bout;

end process;

process( b, dr, en)

begin

if (en='0') and (dr='0') then aout<=b;

else aout<="ZZZZZZZZ";

end if;

a<=aout;

end process;

end rtl;

时序电路

时序电路中,任一时刻的输出信号取决于:

a.当时的输入信号;

b.电路原来的状态,和以前的输入有关;

即:时序逻辑电路具有”记忆”功能。

(1)时钟信号和复位信号

时钟信号:

任何时序电路都以时钟信号为驱动信号;

时序电路仅在时钟信号的边沿到来时,其状态才发生改变。

时钟信号通常是描述时序电路程序的执行条件;

时序电路总是以时钟进程的形式进行描述的,一般有两种方式:

a.进程的敏感信号是时钟信号;

PROCESS (clock_signal)

BEGIN

IF (clock_edge_condition) THEN

signal_out<= signal_in;

:

其它时序语句

:

END IF;

END PROCESS;

(1)只能出现一个时钟信号;

(2)要注明是上升沿或下降沿;

(3)敏感列表中可同时出现时钟和复位信号;

b.用进程中的wait on 语句等待时钟;

PROCESS

BEGIN

wait on (clock_signal) until (clock_edge_condition) signal_out<= signal_in;

:

其它时序语句

:

END IF;

END PROCESS;

(1)只能出现一个时钟信号;

(2)要注明是上升沿或下降沿;

(3)wait on 语句只能放在进程的最前面或最后面

时钟边沿的描述:

上升沿:clk'EVENT AND clk='1' [and clk'last_value='0']

下降沿:clk'EVENT AND clk='0' [and clk'last_value='1']

例如:

IF (clk'EVENT AND clk='1') THEN

WAIT on clk'EVENT UNTIL clk='1';

IF (clk'last_value='0' AND clk'event AND clk='1') THEN

IF (risin_edge(clk)) THEN

IF (clk'EVENT AND clk='0') THEN

WAIT on clk'EVENT UNTIL clk='0';

IF (clk'last_value='1' AND clk'event AND clk='0') THEN

IF (falling_edge(clk)) THEN

时钟电平触发的描述:

高电平触发:IF (clk='1') THEN

低电平触发:IF (clk='0') THEN

复位信号:

同步复位:当复位信号有效且在给定的时钟边沿到来时,触发器才被复位。

同步复位一定在以时钟为敏感信号的进程中。

用IF语句来描述必要的复位条件。

且一定要嵌套在描述时钟边沿条件的IF内。

PROCESS(clock_signal)

BEGIN

IF(clock_edge_condition) THEN

IF(reset_condition) THEN

Signal_out<=reset_value;

ELSE

Signal_out<=signal_in;

┇

END IF;

END IF;

END PROCESS;

异步复位:一旦复位信号有效,触发器立即复位。

首先,在进程的敏感信号表中除时钟外,

还应添上复位信号。

另外,描述复位的IF语句应放在进程的第一条语句位置。

PROCESS(clock_signal, reset_signal)

BEGIN

IF(reset_condition) THEN

Signal_out<=reset_value;

ELSIF(clock_edge_condition) THEN

Signal_out<=signal_in;

┇

END IF;

END PROCESS;

(2)触发器

D触发器

a、基本的上升沿D触发器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY dff1 IS

PORT (clk,d:IN STD_LOGIC;

q:OUT STD_LOGIC);

END dff1;

ARCHITECTURE rtl OF dff1 IS

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

q<=d;

END IF;

END PROCESS;

END rtl

或者:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY dff1 IS

PORT (clk,d:IN STD_LOGIC;

q:OUT STD_LOGIC);

END dff1;

ARCHITECTURE rtl OF dff1 IS

BEGIN

PROCESS

BEGIN

WAIT UNTIL clk'EVENT AND clk='1';

q<=d;

END PROCESS;

END rtl;

b、带异步复位的D触发器

当clr=’0’时,其q端输出被强迫置为“0”。clr 又称清零输入端。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY dff2 IS

PORT (clk,d,clr:IN STD_LOGIC;

q:OUT STD_LOGIC);

END dff2;

ARCHITECTURE rtl OF dff2 IS

BEGIN

PROCESS (clk,clr)

BEGIN

IF (clr='0') THEN

q<='0';

ELSIF (clk'EVENT AND clk='1') THEN

q<=d;

END IF;

END PROCESS;

END rtl;

c、带同步复位的D触发器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY dff4 IS

PORT (clk,clr,d:IN STD_LOGIC;

q:OUT STD_LOGIC);

END dff4;

ARCHITECTURE rtl OF dff4 IS

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

IF (clr='1') THEN

q<='0';

ELSE

q<=d;

END IF;

END IF;

END PROCESS;

END rtl;

d、带异步置位/复位的D触发器

优先级:pset>clr>clk

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY dff3 IS

PORT (clk,d,clr,pset:IN STD_LOGIC;

q:OUT STD_LOGIC);

END dff3;

ARCHITECTURE rtl OF dff3 IS

BEGIN

PROCESS (clk,pset,clr)

BEGIN

IF (pset='0') THEN

q<='1';

ELSIF (clr='0') THEN

q<='0';

ELSIF (clk'EVENT AND clk='1') THEN

q<=d;

END IF;

END PROCESS;

END rtl;

e、带同步置位/复位的D触发器

输入:d、pset、clk、clr

输出:q

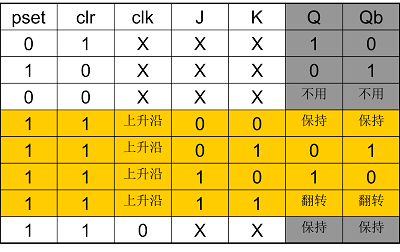

JK触发器

输入:

置位输入pset

复位输入clr

控制输入j和k

s时钟信号输入clk

输出:

正向输出q

反向输出qb

带异步复位、置位功能的JK触发器:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY jkdff IS

PORT (pset,clr,clk,j,k:IN STD_LOGIC;

q,qb:OUT STD_LOGIC);

END jkdff;

ARCHITECTURE rtl OF jkdff IS

SIGNAL q_s, qb_s: STD_LOGIC;

BEGIN

PROCESS (pset,clr,clk,j,k)

BEGIN

IF (pset='0') and (clr='1') THEN

q_s<='1';

qb_s<='0';

ELSIF (pset='1') and (clr='0')THEN

q_s<='0';

qb_s<='1';

ELSIF (pset='1') and (clr='1') and (clk'EVENT AND clk='1') THEN

IF (j='0'AND (k='1') THEN

q_s<='0';

qb_s<='1';

ELSIF (j='1') AND (k='0') THEN

q_s<='1';

qb_s<='0';

ELSIF (j='1') AND (k='1') THEN

q_s<=NOT q_s;

qb_s<=NOT qb_s;

END IF;

END IF;

q<=q_s;

qb<=qb_s;

END PROCESS;

END rtl;

T触发器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY tff IS

PORT(t ,clk : IN STD_LOGIC;

q : BUFFER STD_LOGIC;

qb : OUT STD_LOGIC);

END tff;

注意:端口q的定义

BUFFER为缓冲端口,功能与INOUT类似,

区别在于当需要读入数据时,

只允许内部回读内部产生的输出信号,

即反馈。

ARCHITECTURE rtl OF tff IS

BEGIN

PROCESS(clk,t)

BEGIN

IF (clk'EVENT AND clk='1') THEN

IF (t='1') THEN

q<=NOT q;

ELSE

q<=q;

END IF;

END IF;

END PROCESS;

qb <= NOT q;

END rtl;

RS触发器

(3)寄存器

能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器。寄存器一般由多位触发器链接而成,通常有:锁存寄存器、移位寄存器等。

锁存寄存器74LS374:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY register IS

PORT(d: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

oe,clk: IN STD_LOGIC;

q: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END regiser;

ARCHITECTURE rtl OF register IS

signal q_temp:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(clk,oe)

BEGIN

IF (oe ='0' ) THEN

IF (clk'EVENT AND clk='1') THEN

q_temp <= d;

END IF;

ELSE

q_temp <=“ZZZZZZZZ”;

END IF;

q<=q_temp;

END PROCESS;

END RTL;

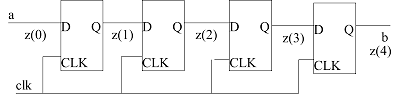

移位寄存器:移位寄存器除了具有存储二进制码的功能以外,还具有移位功能。所谓移位功能就是指寄存器里面存储的代码能够在时钟的作用下进行依次左移或者右移。可以用来实现数据的串—并转换、数值运算以及数据处理等。

串入、串出移位寄存器:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY shift4 IS

PORT (a,clk:IN STD_LOGIC;

b:OUT STD_LOGIC);

END shift4;

Generate Statement

Simplified Syntax

label : for parameter in range generate

[ { declarations }

begin ]

{ concurrent_statements }

end generate [ label ];

label : if condition generate

[ { declarations }

begin ]

{ concurrent_statements }

end generate [ label ];

4位串入、串出移位寄存器描述:

ARCHITECTURE sample OF shift4 IS

COMPONENT dff

PORT (d,clk:IN STD_LOGIC;

q:OUT STD_LOGIC);

END COMPONENT;

SIGNAL z:STD_LOGIC_VECTOR (0 TO 4);

BEGIN

z(0)<=a;

g1:FOR i IN 0 TO 3 GENERATE

dffx: dff PORT MAP (z(i),clk,z(i+1));

END GENERATE;

b<=z(4);

END sample;

不采用元件连接的方法,而采用直接描述方法:

ARCHITECTURE sample OF shift4 IS

SIGNAL z:STD_LOGIC_VECTOR (1 TO 7);

BEGIN

process(clk)

begin

if (clk'EVENT AND clk='1') THEN

z(1)<=a;

z(2)<=z(1);

z(3)<=z(2);

z(4)<=z(3);

b<=z(4);

end if;

end process;

END sample;

串入、并出移位寄存器:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY shift4 IS

PORT (a,clk:IN STD_LOGIC;

q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END shift4;

ARCHITECTURE sample OF shift4 IS

COMPONENT dff

PORT (d,clk:IN STD_LOGIC;

q:OUT STD_LOGIC);

END COMPONENT;

SIGNAL z:STD_LOGIC_VECTOR (4 DOWNTO 0);

BEGIN

z(0)<=a;

g1:FOR i IN 0 TO 3 GENERATE

dffx: dff PORT MAP (z(i),clk,z(i+1));

END GENERATE;

q<=z(4 DOWNTO 1);

END sample;

(4)计数器

记忆时钟脉冲的个数,它是用几个触发器的状态,按照一定规律随时钟变化来记忆时钟的个数。

同步计数器:在时钟脉冲(计数脉冲)的控制下,构成计数器的各触发器状态同时发生变化。

--六进制计数器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY cnt6

PORT(clr, en, clk: IN STD_LOGIC;

qa, qb, qc: OUT STD_LOGIC);

END cnt6;

ARCHITECTURE rtl OF ont6 IS

SIGNAL q: STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS(clk)

VARIABLE q6: INTEGER;

BEGIN

IF(clk'EVENT AND clk='1') THEN

IF(clr='0') THEN

q6 := 0;

ELSIF(en='1') THEN

IF(q6=5) THEN

q6:=0;

ELSE

q6:=q6+1;

END IF;

END IF;

END IF;

q<=CONV_STD_LOGIC_VECTOR(q6, 3);

qa<=q(0);

qb<=q(1);

qc<=q(2);

END PROCESS;

END rtl;

可逆计数器:既可以正向计数,又可以反向计数,故称可逆计数器,常用于控制器设计。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY updn_cnt10 IS

PORT(updn, clr, clk: IN STD_LOGIC;

qout: OUT STD_LOGIC_VECTOR(9 DOWNTO 0));

END updn_cnt10;

ARCHITECTURE rtl OF updn_cnt10 IS

BEGIN

PROCESS(clk)

VARIABLE cnt: INTEGER RANGE -512 TO 511;

VARIABLE dir: INTEGER RANGE -1 TO 1;

BEGIN

IF(updn='1') THEN

dir∶=1;

ELSE

dir∶=-1;

END IF;

IF(clk'EVENT AND clk='1') THEN

IF(clr='0') THEN

cnt∶=0;

ELSE

cnt∶=cnt+dir;

END IF;

END IF;

qout<=CONV_STD_LOGIC_VECTOR(cnt, 10);

END PROCESS;

END rtl;

同步100进制计数器的设计:

Library ieee;

Use ieee.std_logic_1164.all;

Use ieee.std_logic_arith.all;

Use ieee.std_logic_unsigned.all;

Entity h27 is

port(clk:in std_logic;

qa,qb:out std_logic_vector(3 downto 0));

End h27;

Architecture rtl of h27 is

signal qan:std_logic_vector(3 downto 0);

signal qbn:std_logic_vector(3 downto 0);

signal cin:std_logic;

Begin

process(clk)

begin

if (clk’event and clk=‘1’) then

if qan=9 then

qan <= “0000”;cin<=‘1’;

else

qan <= qan+1;cin<=‘0’;

end if;

end if;

End process;

或者:

process(clk,cin)

begin

if (clk’event and clk=‘1’) then

if cin=‘1’ then

if qbn=9 then

qbn <= “0000”;

else

qbn <= qbn+1;

end if;

end if;

End process;

qa<=qan;

qb<=qbn;

End rtl;

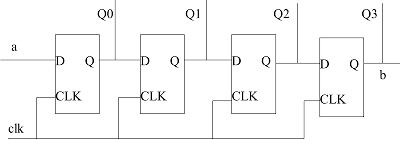

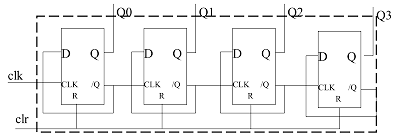

异步计数器:由前一级触发器的输出作为后一级触发器的计数脉冲输入,这样一级一级推动进行计数。这种计数器延迟较大,但结构简单,常用于小型或要求速度不太高的电路中。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY acount IS

PORT(clr, clk: IN STD_LOGIC;

q: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END acount;

四位异步计数器的描述:

ARCHITECTURE rtl OF acount IS

COMPONENT adff

PORT(clk, clr, d: IN STD_LOGIC;

q, qb: OUT STD_LOGIC);

END COMPONENT;

SIGNAL q_temp: STD_LOGIC_VECTOR(4 DOWNTO 0);

BEGIN

q_temp(0)<=clk;

gen1: FOR i IN 0 TO 3 GENERATE

dffx: adff PORT MAP(clk=>q_temp(i), clr=>clr, d=>q_temp(i+1),

q=>q(i), qb=>q_temp(i+1));

END GENERATE;

END rtl;